BONUS SHOW DISTRIBUTION: GSPx, SDR FORUM

# The COTS Technology Authority EMBEDDED SYSTEMS

### EDITORIAL

> SDR: We need it now

### **INDUSTRY ANALYSIS**

- > Product warranties

OCTOBER 2005

# SDR + FPGAs +

SOFTWARE

SCA's evolution links to other specs

HARDWARE

Altera logic secures mil systems

APPLICATIONS

Low-power flash storage

PRODUCT GUIDE

**SBCs for signal** processing

**Need Military Gigabit Ethernet?**

# ET-71000 GigEXTREME™ TCP/IP Offload Engine

|                                                     | GigEXTREME™ | Other TOE Cards | NICs with Partial<br>Offload |  |  |  |

|-----------------------------------------------------|-------------|-----------------|------------------------------|--|--|--|

| Processor Loading*                                  | 5%          | 5%              | 50% to 70%                   |  |  |  |

| RTOS Support                                        | <b>~</b>    | <b>~</b>        | -                            |  |  |  |

| No Application Modification or Recompilation Needed | <b>✓</b>    | -               | ~                            |  |  |  |

| No Use of Upscreened<br>Commercial Components       | <b>✓</b>    | _               | _                            |  |  |  |

| Military Rugged                                     | <b>✓</b>    | Some            | Some                         |  |  |  |

| IPv6 Capable                                        | <b>~</b>    | _               | -                            |  |  |  |

\* Processor loading measured for the TCP/IP receive network task on a 1 GHz Power PC host.

Sweden/Denmark

Benelux Finland

DDC (United Kingdom) LTD. DDC Electronique

England Tel: +44 (1635) 811140

Switzerland Spain Norway

**DDC Europe** Tel: +33 1 41 16 34 24

+41 41 748 32 32

**DDC Electronik GmbH**

Germany Tel: +49 (0) 89 - 15 00 12 - 11 +44 1635 811140 +27 11 882 6836/7

East Europe Russia Federation +7 812 389 0104

ISO 9001 REGISTERED

# ICS-572. Out of this world

Just because you're short of space, you shouldn't be short on features.

The ICS-572 2-channel PMC module may be designed specifically for today's small-form factor, lightweight PCI systems, but that doesn't mean it compromises on functionality.

Combining the best in 14-bit ADC and DAC technologies with a high-density, high-speed, user-programmable FPGA, the ICS-572 delivers industry-leading cost, size and performance. It's ideally suited for multimission, high bandwidth radar and communications applications that need to both transmit and receive.

With support for Windows, Linux and VxWorks, and comprehensive application development support from ICS, the ICS-572 offers unparalleled flexibility and speed of deployment. As they say: small is beautiful.

ICS-572. Great leaps forward.

RSC# 3 @www.mil-embedded.com/rsc

# VOLUME 1 NUMBER 2 OCTOBER 2005

www.mil-embedded.com

# **DEPARTMENTS**

# **Industry Analysis**

- 8 What has happened to product warranties?

By Jerry Gipper

- 10 Beep, configure, fire By Don Dingee

- 12 Trends in military computing By Joe Pavlat

# In the System

- 16 FPGAs gearing up to dominate DSP applications By Duncan Young, SBS Technologies

- 24 Editor's Choice Products

# Crosshairs Editorial

62 We need SDR *now*By Chris A. Ciufo

56 New Products

By Sharon Schnakenburg

# **Product Selection Guide**

50 Single board computers for DSP and reconfigurable computing

# **EVENTS**

# SDR Forum

Nov. 14-18 • Garden Grove, CA www.sdrforum.org

# **Embedded Connect**

Nov. 17 • Santa Clara, CA

### COVER

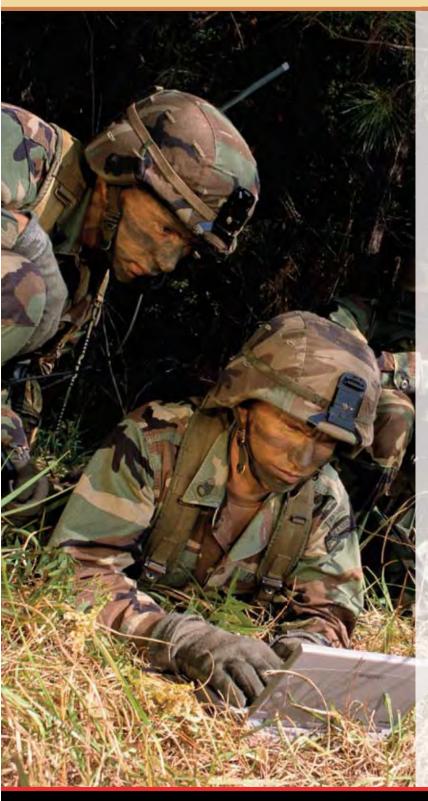

A Humvee providing communication sits atop a lonely hill half covered in desert pattern cami netting. (Photo courtesy of U.S. Marines by Lance Cpl. Jem J. Hamilton).

### PRODUCT

Using internal PC/104-Plus modules, the Talon 8400 by GE Fanuc Embedded Systems is a self contained PC designed for rugged applications from -20 °C to +50 °C.

Published by:

4 / October 2005 MILITARY EMBEDDED SYSTEMS

©2005 Military Embedded Systems

# **FFATURES**

# HARDWARE:

- Why convert to a SAASM-based GPS?

- By Ron Holm, Symmetricom

- 25 Enabling military design security with high-performance FPGAs

By Joel Seely & Jie Feng, Altera

# **SOFTWARE: Software Defined Radio**

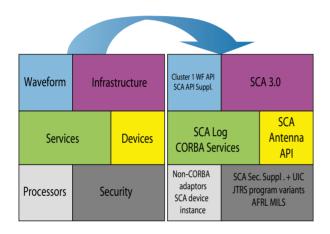

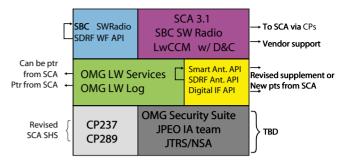

28 Software communication architecture: Evolution and status update

By Jeff Smith, Ph.D., David Murotake, Ph.D., and Antonio Martin, SCA Technica

34 Cognitive radios: The future of SDR technology

By Bruce Fette, Ph.D., General Dynamics C4 Systems

Mapping waveforms to systems: What would a wideband networking waveform system require?

By Kevin Maier, Spectrum Signal Processing

# **APPLICATION: Performance enhancements**

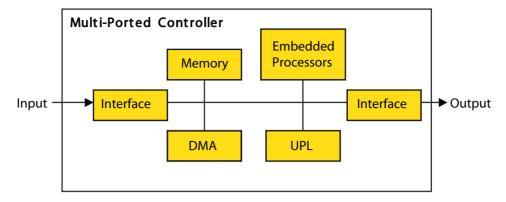

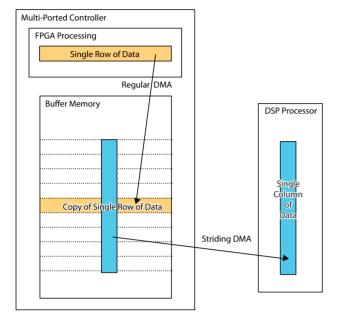

42 FPGA memory controllers improve DSP performance

By Richard M. Matthews, Micro Memory

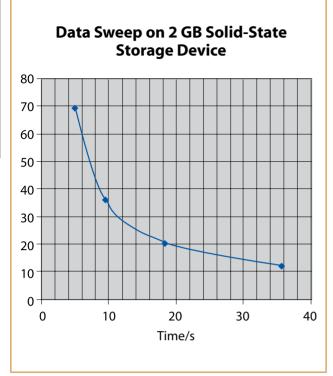

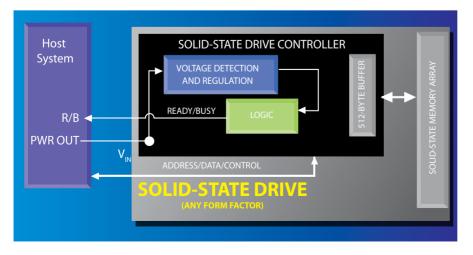

46 Tapping into solid-state storage benefits for low-power and small form factor applications

By Gary Drossel, Silicon Systems

# E-LETTER

# WWW.MIL-EMBEDDED.COM/ELETTER

Net-centric computing: Architecting a distributed data-management infrastructure

By Bert Farabaugh, RTI

FLOSS helps you take control of your bytes

By Robert Dewar, AdaCore

Please visit us online for the complete list of articles

# WEB RESOURCES

# Subscribe to the magazine or E-letter:

www.opensystems-publishing.com/subscriptions

"Great in a lab, so how about in a UAV?"

RSC# 5 @www.mil-embedded.com/rsc

Motorola makes products that are compute dense and famous for longevity like VMEbus and CompactPCI® boards and chassis using various PowerPC® and Intel® processors. They're produced commercially in significant volumes, so they're more competitively priced. How do you take full advantage of that in a field application?

# COTS by Motorola. Mods by Arrow.

That's where Arrow comes in.

We have one of the broadest

line cards in the industry and

the expertise to integrate

disparate systems, hardware,

and software with extreme

efficiency. We've gotten it right

for thousands of clients for

more than 29 years.

And Arrow teams with companies like Carlo Gavazzi Mupac, recognized across the industry for packaging and ruggedizing to meet military specs.

Reliability. Functionality, Flexibility. It's like getting full customization for a fraction of the cost. Yes. That'll fly.

0EM Computing Solutions 888-427-2250 www.arrownacp.com

# OpenSystems Publishing

Advertising/Business office: 30233 Jefferson Avenue St. Clair Shores, MI 48082

Tel: 586-415-6500 Fax: 586-415-4882

## **BUSINESS OFFICE:**

**Vice President Marketing & Sales**

**Patrick Hopper**

phopper@opensystems-publishing.com

**Business Manager**

Karen Layman

## **ADVERTISING GROUP:**

**Vice President Marketing & Sales**

Patrick Hopper

phopper@opensystems-publishing.com

Senior Account Manager

Dennis Dovle

ddoyle@opensystems-publishing.com

**Account Manager**

Tom Varcie

tvarcie@opensystems-publishing.com

**Print and Online Marketing Specialist**

**Christine Long**

clong@opensystems-publishing.com

**Advertising/Marketing Coordinator**

Andrea Stabile

astabile@opensystems-publishing.com

**European Bureau Chief**

Stefan Baginski

sbaginski@opensystems-publishing.com

**Account Manager**

Doug Cordier

dcordier@opensystems-publishing.com

### COMMUNICATIONS GROUP:

Patrick Hopper

phopper@opensystems-publishing.com

**Christine Long**

clong@opensystems-publishing.com

# **EMBEDDED GROUP:**

**Dennis Doyle**

ddoyle@opensystems-publishing.com

**Doug Cordier**

dcordier@opensystems-publishing.com

### **MILITARY GROUP:**

Tom Varcie

tvarcie@opensystems-publishing.com

Andrea Stabile

astabile@opensystems-publishing.com

# **INTERNATIONAL SALES:**

Stefan Baginski

sbaginski@opensystems-publishing.com

For reprints and PDFs call the sales office: 586-415-6500

# OPENSYSTEMS PUBLICATION

# Military and Aerospace Group

- DSP&FPGA Product Resource Guide

- DSP-FPGA.com

- DSP-FPGA.com E-letter

- Military Embedded Systems

- Military Embedded Systems E-letter

- PC/104 Embedded Solutions

- PC/104 Embedded Solutions E-letter

- PC/104 & Small Form Factor Catalog

- VMEbus Systems

- VMEbus Systems E-letter

Group Editorial Director Chris A. Ciufo

cciufo@opensystems-publishing.com

Managing Editor Bonnie Crutcher

bicrutcher@opensystems-publishing.com

Senior Editor (columns) Terri Thorson

tthorson@opensystems-publishing.com

Assistant Editor Sharon Schnakenburg

sschnakenburg@opensystems-publishing.com

**European Representative** Hermann Strass

hstrass@opensystems-publishing.com

Art Director Steph Sweet Senior Web Developer Konrad Witte

Graphic Specialist David Diomede Circulation/Office Manager Phyllis Thompson

subscriptions@opensystems-publishing.com

# OpenSystems Publishing

Editorial/Production office:

16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

Tel: 480-967-5581 Fax: 480-837-6466 Website: www.opensystems-publishing.com

**Publishers** John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial Rosemary Kristoff

### Communications Group

Editorial Director Joe Pavlat **Assistant Managing Editor** Senior Editor (columns) **Technology Editor**

Anne Fisher Terri Thorson Curt Schwaderer European Representative Hermann Strass

# Embedded and Test & Analysis Group

**Editorial Director Editorial Director** Associate Editor Senior Editor (articles) Technical Editor

Jerry Gipper Don Dingee Jennifer Hesse Terri Thorson Chad Lumsden **Bob Stasonis**

Special Projects Editor European Representative Hermann Strass

Canada return address: WDS, Station A, PO Box 54, Windsor, ON N9A 615

Military Embedded Systems is published six times a year by OpenSystems Publishing LLC., 30233 Jefferson Ave., St. Clair Shores, MI 48082. Subscriptions are free, upon request in writing, to persons dealing with or considering Military Embedded Systems.

For others inside the US and Canada, subscriptions are \$34/year. For 1st class delivery outside the US and Canada, subscriptions are \$60/year (advance payment in US funds required).

POSTMASTER: Send address changes to Military Embedded Systems 16872 E. Ave of the Fountains, Ste 203, Fountain Hills, AZ 85268

# And Designed, Built and Tested by Aitech.

Designing and building board level products and sub-systems for space applications is tough enough. Doing it in a true COTS environment is even tougher. It takes a very special company to do it right – and that company is Aitech. We not only designed and built the world's first harsh environment, open architecture VMEbus boards more than two decades ago, but we're fully qualified for use in today's most hostile environment – space.

The only COTS company... Aitech is the only COTS company in the world that offers embedded products for space applications with this combination of features: • Designed and qualified specifically by us for space • Radiation-tolerant throughout • On-board triple redundant memory • Rad-hard SOI (silicon on insulator) ASICs • Single event effects and total dose radiation survivability

Total space applicability... Aitech embedded products and sub-systems for space are ideal for Low, Medium and High Earth Orbit applications, lunar and Mars robotic vehicles and much more. Our products are used in the Space Shuttle, MIR Space Station, International Space Station and other high profile satellite programs where highest performance and reliability are required.

Real space-qualified COTS... not custom off-the-shelf...but commercial off-the-shelf. COTS the way it's supposed to be!

We don't compete with you... some embedded companies try to be systems integrators. We don't. We deliver board-level product and integrated sub-systems for space (and military/aerospace) applications. We leave the systems integration to the companies that do it best...like yours!

We have what you need... from a full range of high performance, low cost, rad-tolerant, space-qualified CompactPCI SBCs, peripheral I/O boards and PMCs, memory boards and enclosures...to complete radiation and qual-testing, component obsolescence risk mitigation, lifecycle support and program management capabilities — with all the economy-of-scale advantages of off-the-shelf products.

Make us prove it... we can and we will. Call or visit us on the web. Embedded space is our space.

# Aitech Defense Systems, Inc.

9301 Oakdale Avenue Chatsworth, CA 91311 email: sales@rugged.com Toll Free: 888-Aitech8 - (888) 248-3248 Fax: (818) 718-9787 www.rugged.com

# **Industry Analysis**

# What has happened to product warranties?

By Jerry Gipper

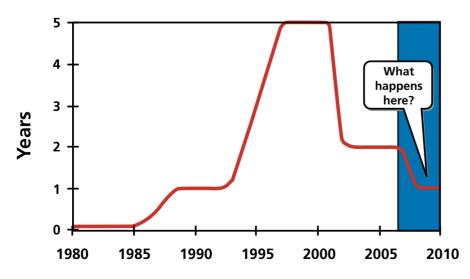

ost embedded electronic hardware components come with a standard product warranty. If a board fails, you contact the supplier, arrange a repair or exchange, ship it to the repair center, and await the repaired or replaced product. This is a rather routine process amongst all suppliers worldwide. In the case of most VME, CompactPCI, and embedded motherboards, today's warranties range from one to three years in duration.

There used to be a time when warranties from many suppliers were five years or in some cases, "lifetime" (Figure 1). What ever happened to those warranties? Why are they not as common? In the early 1990s there was a lot of noise in the industry about long or lifetime warranties. Press releases were distributed touting the warranty terms, and warranties were highlighted in advertisements. Suppliers were very proud of their product reliability and were willing to stand behind their products.

A quick check today of the same product types shows typical warranty periods of only two years, with a few as long as three years. Certainly these are shorter than "lifetime." Has something happened to the reliability? Has the cost of quality risen too high to absorb in competitive pricing strategies?

This change in warranty periods started quietly happening as companies were recovering from the dot-com bust in 2001. No embedded technology suppliers publicly "announced" their shorter warranty periods. In fact, the reduced warranty periods did not hit home until a problem occurred and a product needed repair. Did suppliers reduce prices to reflect the shortened warranty periods? I would venture to guess prices were not reduced since suppliers were already under extreme margin pressures during those times.

Some possible explanations exist as to why warranties greater than two years are no longer typical. Any one or more of the following are key factors in determining warranty terms and pricing:

- Increased cost of quality: By definition, the Cost Of Poor Quality (COPQ) consists of costs generated as a result of producing defective material. Additional cost includes all the labor cost, rework cost, disposition cost, utilities cost, manufacturing cost, and material cost that has been added to the unit up to the point of rejection. It also includes the cost of lost opportunity due to the loss of resources used in rectifying the defect. The cost of lost opportunity means lower revenue and profit, potential loss of market share, and a lower service level to customers. All areas of cost in COPQ have increased in past years.

- Speed of technology: In general, the technologies used in embedded computing systems are still relatively new. New technologies evolve rapidly, and rapidly evolving technologies have a shorter product life cycle. Getting the quality to an acceptable level can be a challenge at best with many of the newer technologies. Do designers and manufacturers always fully understand the quality issues of one technology before moving on to the next?

- Pursuit of quality: With products' shorter life cycles, perhaps the race to have the best and most optimized set of features at a competitive price has pushed quality into the backseat. Products today have manufacturing lives less than three years in duration. In most cases, the quality is not fully optimized in that short of a life cycle. Suppliers move on to the next generation before they really get the kinks out of the existing products. Sometimes designers may take shortcuts or use unproven design elements to meet time-to-market pressures. With the low quantities and high mix of the embedded space,

# Warranty Length

Figure 1

# Industry Analysis -

it is hard to spend too much time on quality for any single product line. Is enough simulation and accelerated life testing being done?

■ Lost the recipe: Perhaps manufacturers simply "lost the recipe" when changing manufacturing locations as mergers occurred or manufacturing was transferred offshore to large, high-volume contract manufacturers to save costs. The embedded industry tends to

build products in small lots with a high mix of different types and product versions. The manufacturing efficiency is never very high in these situations. Moving to a high-volume, low mix manufacturing facility only frustrates the manufacturing process in these cases. As a result, quality suffers immensely. Lower quality levels mean higher warranty costs and loss of ability to absorb these costs in competitive prices. Most manufacturing operations are great at

building high-quality products, and vendors fully understand the nuances of quality manufacturing; however, it takes high repetitions of the same steps and processes to really reach the best quality levels.

■ Service as a profit center: Maybe the answer is as simple as using warranties as a way to increase the revenue stream. Most embedded board suppliers have extensive repair and service centers. Removing the

cost of the warranty from the product cost and making it a separate price line item is a way for the service centers to improve their revenue streams and justify their existence. It does make it easier to develop custom and innovative service programs that better fit the customer's needs.

What is going to happen to warranty terms in the future? It is possible that the Restriction of the use of certain Hazardous Substances (RoHS) or the Waste from Electric and Electronic Equipment (WEEE) initiatives being driven out of Europe and Asia will force further tightening of warranty terms. Suppliers may use this as the compelling event to tighten the warranty programs even more. Two-year warranties could easily become one-year warranties in the next one to two years.

However, all is not lost as many suppliers in the embedded industry offer various extended warranty programs that can be customized to meet the specific needs of consumers. These programs have options for warranty periods and coverage that can help manage costs for the lifetime of a program. Extended warranties are insurance against a future failure. Be sure to check out all your options when planning lifetime costs for your products.

For more information, you may contact Jerry directly at jgipper@opensystems-publishing.com.

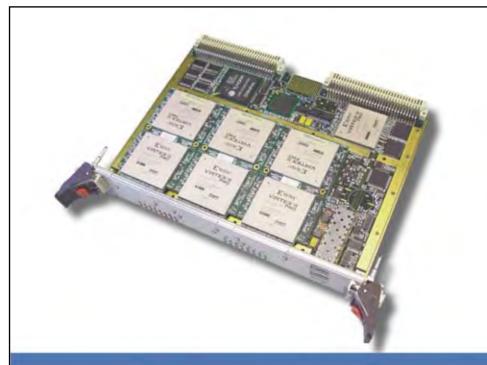

Proven COTS Solutions from the FPGA Computing Experts

VME, cPCI, PCI and PCI-104 COTS Hardware

Systems Software and Development Tools

To find out more and register for the latest Virtex-4 product information visit - www.nallatech.com/capability

North America Toll free: I-877-44-NALLA EMEA & ROW Phone: +44 (0) 1236 789500

# Industry Analysis

# Beep, configure, fire

By Don Dingee

ilitary planners are now talking in terms of plug-and-fight capability. This is a spin on the old personal computing term plug-and-play – catchy, but outdated. As a marketing person at heart, I can't help but suggest an updated term that better describes what we see taking place and what elements are going into this capability.

Most of us have seen some version of the movie scene where the condemned prisoners are paraded out in blindfolds, lined before a wall, and a firing squad is issued the familiar cliché "Ready, aim, fire!"

Today, with electronics driving most combat systems, a more appropriate term for the plug-and-fight process would be "Beep, configure, fire!"

# Beep - Join the network

For today's warfighter, there is a wealth of information and intelligence available in real time as close as the nearest network. Sensor and command data fused into the network from a variety of modes and locations enable a tactical system to quickly access reliable information on the mission plan, threat situation, and the configuration of neighboring defense systems.

"Today, with electronics driving most combat systems, a more appropriate term for the plug-and-fight process would be 'Beep, configure, fire!'"

Recently, I visited a friend in the San Francisco Bay area, and he was showing me his new Bluetooth-enabled phone and headset. He commented that he could not help but notice that when he wears the headset while driving, especially on the freeways, he hears frequent beeps as the headset attempts to connect with devices in neighboring vehicles. It's almost *too* easy to connect to a network now.

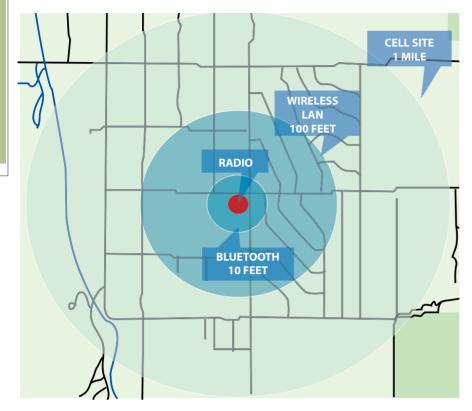

Short-range wireless networks provide a continuous network tone and have made it easy to connect quickly to a wide variety of devices. Technologies such as Bluetooth, Wi-Fi, Ultrawideband, Wireless USB, and the longer-range WiMax may soon be enabled with a security layer, enabling their use in defense applications. For now, defense networks using Software Defined Radio (SDR) technologies fit the bill.

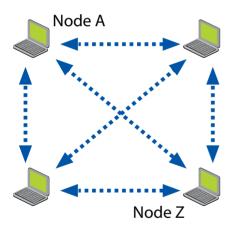

Planners talk of systems fitting into a *netted*, *distributed* force. Whether wired or wireless, today's defense systems-of-systems are built around network-centric designs and rely on being able to join the network quickly.

# **Configure – Compute for effect**

Reconfigurable computing has advanced an incredibly long way in recent years. Advances in System-on-Chip (SoC) technology combining processing with FPGAs allow designers to optimize and adapt computing hardware to better fit immediate requirements. Linux-based open system architectures allow *clusters* (just another term for systems-of-systems) to add distributed nodes easily, enabling distributed processing and sensor fusion capability quickly and reliably.

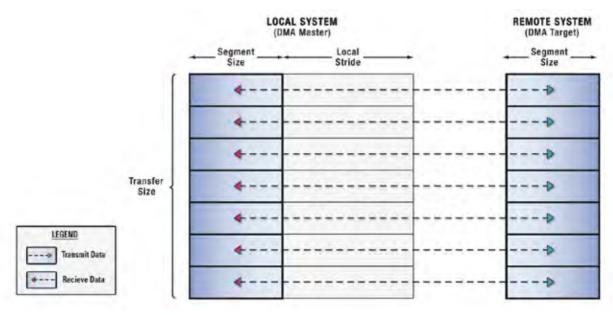

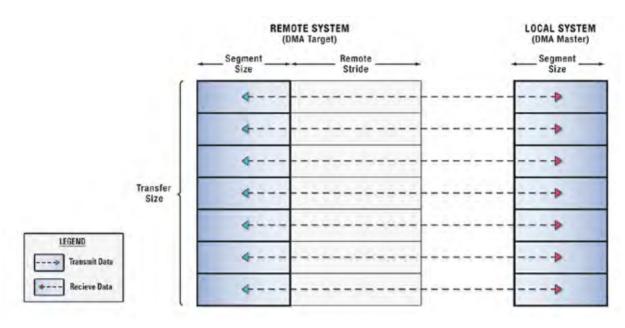

It's the intersection of processor, network fabric, and operating system in a reconfigurable form that becomes interesting. One example of this is the CoSine from Micro Memory. Built on the Xilinx Virtex-4 FPGA family with VxWorks running on two PowerPC 405 cores, it includes connectivity for serial RapidIO or PCI Express, a corner-turning Direct Memory Access (DMA) engine to aid in data movement, and a user-programmable area for signal processing algorithms. (Refer to the Micro Memory article on page 42 in this issue.)

Additionally, advances are being made in Linux on FPGA platforms. The University of Queensland in Australia recently secured a contract for NASA's Reconfigurable Scalable Computing (RSC) project, building from a starting point in which a version of uClinux is adapted to the Xilinx MicroBlaze soft-core processor. The ultimate goal will be to remotely (as in ground-to-space) partially reprogram FPGAs on the fly.

We may see that general-purpose processors ultimately give way to reconfigurable processors in defense applications, both for functional and life-cycle reasons. Teamed with the University of Southern California and using IBM Cu-08 90 nm process technology, Raytheon's Morphable Networked Micro-Architecture (MONARCH) project targets April 2008 for a device that can alternate instantaneously between front-end (streaming) and back-end (threaded) processing.

According to Jack Kelble, president of Raytheon Space and Airborne Systems, "In the past, a bank of processor boards accepted information and another bank processed it." He added, "Now a tiny but highly sophisticated device a fraction of the size will perform both functions with unprecedented speed, power, and capacity to store and process a vast amount of data." MONARCH is expected to perform in a single chip or SoC role, possibly significantly reducing the number and types of processors required for computing systems. In the latter application, it will be able to process incoming and outgoing data while analyzing it.

# Fire – With open weapons

Using technologies such as these, networked, reconfigurable weapons systems are beginning to emerge as the norm. Initiatives including the Modular Open Systems Approach (MOSA) spon-

sored by The Open Systems Joint Task Force within the US Department of Defense continue to set higher expectations.

Openness in new acquisitions is being demanded as seen in these comments from Lieutenant General Ronald E. Keys in February 2005: "We've got to get to this thing called the 'compatible open architecture.' I've got to be able to truly plug-and-play, and it's got to plug-and-play better than Microsoft. It's actually got to plug, boot up, recognize, and work ... So don't bring me stuff that's not compatible because I'm not going to be happy."

Large combat systems already architecting around plug-andfight concepts include the Medium Extended Air Defense System (MEADS), Future Combat Systems (FCS), and the Littoral Combat Ship (LCS).

MEADS is the US Army's next-generation replacement for Nike Hercules, Hawk, and Patriot air-defense missile systems, designed from the ground up to move with ground forces and interoperate with other allied forces. It relies heavily on networking and distributed intelligence to achieve its mission. A MEADS system has the capability to command a fleet of distributed missile launchers while simultaneously detecting and tracking hostile forces and targets. There is a key tactical advantage to this distributed design: The missile launchers can be located well away from the ground radar and the battle management units, reducing the risk of detection of the launchers. This tactical advantage also opens the possibility to transfer command and control of the launchers and missiles to a neighboring battle management unit, while some management systems are offline for whatever reason.

FCS isn't a single system but rather a blended system-of-systems intended to transform the US Army's fighting capability. Underlying FCS is a software architecture called Fire Control - Node Engagement Technology (FC-NET). FC-NET provides an adaptable, flexible architecture that modularizes the interaction between the technical weapon system (the intelligence that controls and guides the weapon) and the tactical information systems. This enables weapon systems to readily join the command fabric to get the information they require.

Another plug-and-fight system is LCS. It's being designed to work in three primary mission areas for the US Navy, including mine countermeasures, anti-submarine warfare, and anti-surface warfare, presumably with anti-air, self-defense capability in each role. This is being accomplished through the design of mission packages that fit into the sea frame and adapt the capability to the desired mission area. Opensystems architecture and modular, networked subsystems are again the key to success, and the notion of being able to reconfigure the system for the role at hand is prominent in the architecture.

### Open doesn't mean big

Creating new systems-of-systems isn't necessarily about using big computers. From the looks of things, it could be just the opposite, using networks of relatively small processors tied together wirelessly with very intelligent software and combining these systems into larger systems.

Researchers at the University of Essex are working on a concept called the gridswarm, where small Unmanned Aerial Vehicles (UAVs) capable of speeds up to 120 mph fly in formations similar to the flocking behavior of small birds. In the prototype, these aircraft are connected by a Bluetooth mesh driven by Linux compute modules from Gumstix. These tiny modules run Linux 2.6 on 400 MHz Intel Xscale processors with 64 MB DRAM and 4 MB Flash, along with USB, serial, and optional Bluetooth interfaces. It's a great example of small systems fitting into larger systems fitting into still larger systems with aggregated intelligence.

Rapid developments in wireless networking, reconfigurable computing, and network-centric weapons systems are going to spawn new innovations quickly. The results should also reduce the long-term costs of weapons procurement, enabling easier upgrades and reducing the impact of obsolescence by allowing subsystem level replacements.

I'll be sure to tell my friend the next time I see him that when he hears a whole bunch of beeps in rapid succession on his Bluetooth headset, he should duck. It could be a UAV gridswarm reconfiguring just overhead, and hopefully they are unarmed and peace loving.

If you happen to see a gridswarm, or other interesting developments that beep and configure, drop me a line.

For more information, contact Don at ddingee@opensystemspublishing.com.

RSC# 11 @www.mil-embedded.com/rsc

# **Industry Analysis**

# **Trends in military computing**

By Joe Pavlat

# A changing landscape

These are good times for designers of military computer systems, as the range of choices and the breadth of applications and requirements is greater than ever before. Traditionally, military electronics have been extremely expensive, usually purpose-designed and uniquely built for each application. Systems often do not communicate with each other, making future net centric warfare difficult. Reuse of hardware and software has been the exception rather than the norm, and design cycles historically have been long and expensive. Industry insiders often talk about the large "flywheel" in the military computer business, meaning that development cycles are long, and revenues are often years away. The one open standard embraced for military applications, the VMEbus, arguably has been widely accepted not for its blazing performance but rather because the standard was first published more than 20 years ago a veritable lifetime for the rest of the computer industry.

The flywheel is still quite large, but it is rotating a bit more quickly these days. Open industry standards are becoming more popular. Former Secretary

of Defense William Perry's famous COTS directive was a factor, but the same development cost and time-to-deployment pressures that affect the commercial computer world affect military suppliers. Two PCI Industrial Computer Manufacturers Group (PICMG) standards, PICMG 1.0 (PCI-ISA Passive Backplane, 1994) and PICMG 2.0 (CompactPCI, 1995), were released 11 and 10 years ago respectively, and are used for a variety of military applications worldwide.

# A wide range of open standards

PICMG's first published specification, the PCI-ISA Passive Backplane Specification released in 1994, is being used in a wide range of applications, including the onboard fire control computer for the M109 Palladin self-propelled howitzer used extensively in Operation Iraqi Freedom. Companies such as BES Systems Ltd. in Israel offer a complete range of ruggedized airborne, vehicle, and naval computers compliant to the PICMG 1.1 specification, additionally providing compliance to military standards including MIL-STD-810E, which dictates tough requirements for shock, vibration, humidity, fungus, salt and dust, and fog.

Released in 1995, the CompactPCI standard was developed for ruggedized industrial applications. It offered then state-of-the-art performance, based on ubiquitous PCI silicon available from virtually every microprocessor and peripheral chip manufacturer. It was based on the same IEEE 1101.1 mechanical standard used by VME, and it became very popular for communications applications worldwide. Defined for both 3U and 6U form factors, the 6U size became popular for the vast majority of communications applications, which needed every square inch of real estate for components. The 3U form factor has historically been used largely for instrumentation and some industrial automation applications, but was not as widely embraced as the larger 6U form factor.

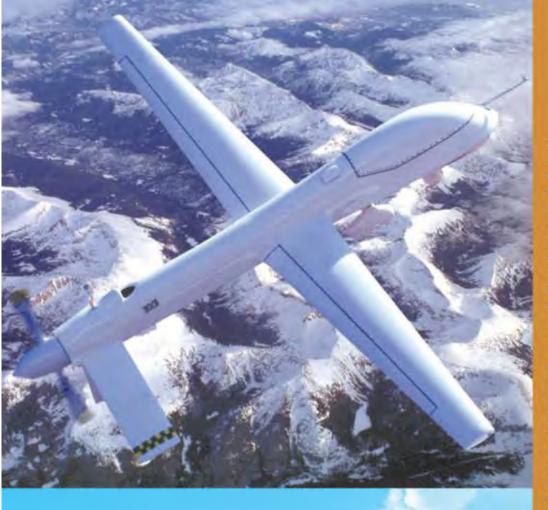

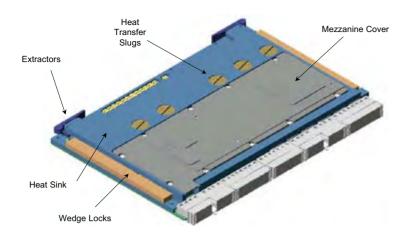

This has been changing over the last few years in a dramatic fashion. Specially ruggedized 3U CompactPCI products are being used for a wide variety of airborne, vehicle, and even space-based systems. One example is the AVC-CPCI 3009 system offered by SBS Technologies, developed for Unmanned Aerial Vehicle (UAV) applications (see Figure 1, photo courtesy of SBS Technologies, Inc.). Its integrated frame grabber and MPEG-4 image compressor connect directly to the airframe's onboard camera, forwarding data in real time to war planners on the ground.

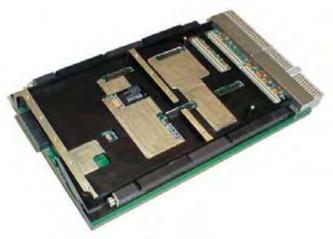

Systems are also going into space. Aitech's S950 3U CompactPCI SBC is conduction-cooled and offers a PowerPC 750FX CPU (see Figure 2, photo courtesy of Aitech Defense Systems, Inc.). It is rated to operate in Low Earth Orbit, Geosynchronous Orbit, and Mars Terrestrial environments.

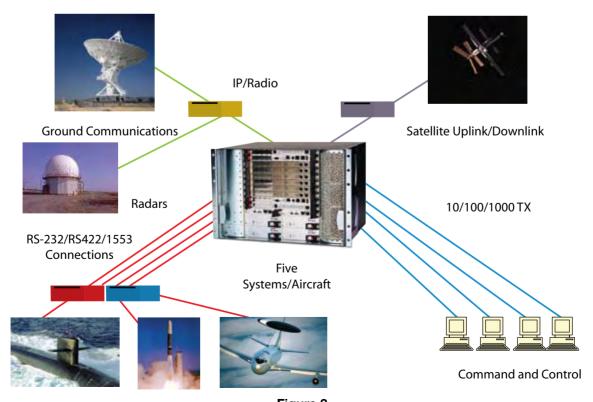

The 6U CompactPCI systems are also being used for military applications. Performance Technologies, Inc. builds a sophisticated Mission LAN System using the PICMG 2.16 CompactPCI Packet Switched Backplane standard. Intended to be part of a National

Figure 1

# Industry Analysis -

Figure 2

Command Center aboard a heavily modified Boeing 707 aircraft known as the *TACAMO*, the system maintains communication and control in the event that other command centers are damaged or destroyed. It provides networking and routing within the aircraft, handling packetized radio, satellite, radar, and laser transmissions, and ties together different systems on the plane (see Figure 3, photo courtesy of Performance Technologies, Inc.).

Performance Technologies has also developed a unique hybrid CompactPCI/

VME system for use in the Global Hawk UAV (see Figure 4, photo courtesy of Performance Technologies, Inc.). This computer provides near real-time high-resolution images and intelligence to field commanders in theater or across the world. Multicast image streams can be ordered by a commander in a control room or a soldier on the ground in the next valley, providing vital current information and situational awareness. The CompactPCI boards are conduction cooled and compliant with the ANSI/VITA 30.1 specification (2 mm connector practice for conduction-cooled Eurocard systems).

# Better architectures hit the ground

One hears a great deal about transforming the military from the current platformcentric approach to network-centric operations. The underlying computer technologies, including chips and software, are also undergoing fundamental change, and it is good news for designers and users of military computers.

Most backplane interconnect technologies, including VME and CompactPCI, are based on chip-level interconnects that were intended for planar motherboards. Hot swap was not an integral part of these interconnects, and their parallel nature has meant that any board plugged into the backplane could cause the entire system to fail if it failed. Full 2N redundancy was often the only solution. Focus was placed on reliability instead of the much more useful concept of availability because parallel bus architectures just do not adapt well to high availability designs, which require system management and failure domains of a single board. Also, as core chip voltages go ever lower, the notion of distributing chip supply voltages often means that parallel backplanes are required to produce hundreds, or even thousands, of amps of current for large systems.

# **Industry Analysis**

Figure 4

This is changing for the better. Primarily, in order to increase data transfer speed, the microprocessor industry is moving rapidly towards switched serial interconnect technology, popularly known as switch fabrics. This technology reduces the speed-robbing capacitance typical of a parallel bus architecture with instantaneous point-to-point interconnects. Not only do these interconnects increase data transmission speed one or two orders of magnitude, which is important for military applications such as imaging, they can, if properly designed, reduce the failure domain to a single board or Field Replaceable Unit (FRU). They also dramatically improve the scalability of military systems, as the same packetized data format used over the backplane can be used between boxes or systems in a large network. Switched fabric Ethernet-based backplane standards, first introduced to the world in 2001 in the PICMG 2.16 Specification, are beginning to be used for military applications.

Additionally, power distribution concepts are changing with an emphasis toward shipping higher voltages across backplanes in order to reduce the ever-increasing currents required by Moore's Law. (We'll save cooling problems for another time.) Localized power conversion is the norm in standards like AdvancedTCA and PICMG's recently ratified advanced mezzanine card standards.

An entire book could be written about software development, but as much as advances in this arena seem to trail hardware progress, a few things can be said. Spurred by the wide adoption of the PCI bus 10 years ago, military board suppliers are increasingly being freed from the need

to write and maintain cumbersome Board Support Packages (BSPs), which often need updating every time a chip on the board changes revision. The Application Programming Interface (API) approach moves that responsibility to the chip supplier and operating system, making systems easier to upgrade and maintain. Expensive RTOSs are beginning to give way to less expensive and increasingly powerful OSs such as Real-Time Linux and Carrier-Grade Linux.

# Notions are changing

In the commercial communications sector, the distinction between datacom and telecom is all but gone as the world's infrastructure moves towards packet-based communications. Military infrastructure, at least in the US, is joining the movement. Major initiatives, such as the Department of Defense's Warfighter Information Network Tactical (WIN-T) program, are based on commercial communication technologies, including secure wireless networks, Voice over Internet Protocol (VoIP), PCS cellular services, and ATM data transport. PDAs, laptops, and tablet computers are widely used in American command centers worldwide, and e-mail is as ubiquitous and important as it is in the civilian sector. The old notions about ruggedized military computers being completely customized boxes milled out of large bars of aluminum are changing. And they are changing for the better as the flywheel spins faster.

For more information, contact Joe at jpavlat@opensystems-publishing.com.

RSC# 1402 @www.mil-embedded.com/rsc

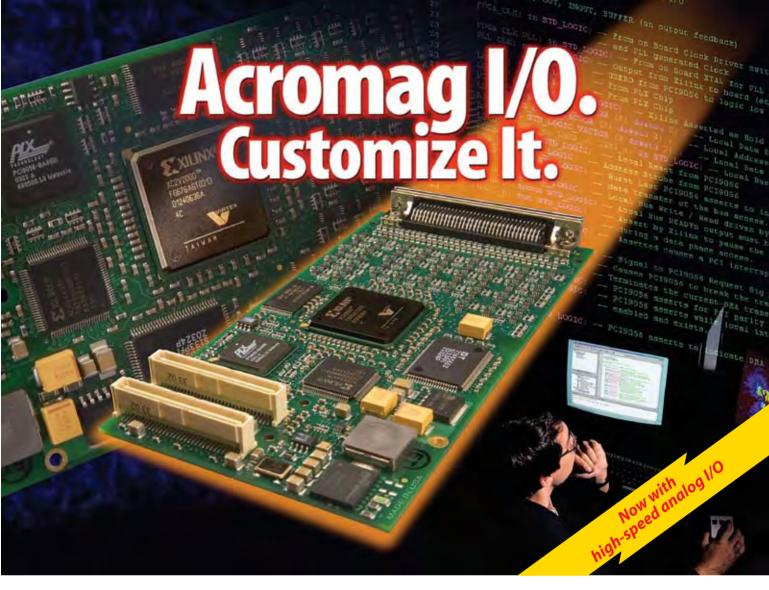

# Acromag introduces affordable FPGA I/O. For ALL your projects.

s an engineer, your projects are unique, ever-changing, and budget-bound. That's why our new PMC modules give you an affordable solution to create custom I/O boards.

But if you thought FPGA computing was only for top-end applications, think again. Our PMCs are ideal for protocol conversion, simulation, in-circuit testing, and much more. So why settle for generic I/O when you can design exactly what you need while staying in budget and reducing your time to market?

- Virtex®-II FPGA with 500K, 2M or 3M system gates

- 1Mb on-chip RAM, 9Mb on-board SRAM

- Fast PCI with 32-bit. 66MHz dual DMA

## Cost-effective custom I/O

Choose from a variety of I/O configurations:

- Digital I/O: TTL, RS422, or LVDS I/O

- Analog I/O: four 20 or 65MHz A/D and two D/A

# Faster time to market

Why waste precious time building a board from scratch? Our new FPGA modules let you process your I/O signals any way you want. Quickly.

# Flexibility to meet unexpected challenges

Acromag FPGA I/O will help you bring your projects in on time and under budget. And with

FPGAs, you'll be ready to adapt to all the inevitable changes. Thinking about FPGA I/O?

www.acromag.com 800-881-0268 or 248-624-1541

# In the System

# FPGAs gearing up to dominate DSP applications

By Duncan Young

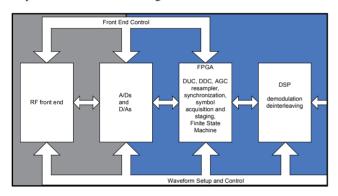

AltiVec PowerPCs have enjoyed dominance in high-end military signal processing applications such as Software-Defined Radio (SDR) and video/image compression. But FPGAs, with their inherent parallelism and reprogrammability, are fast becoming prevalent and easily fit on smaller boards such as PCI Mezzanine Cards (PMCs).

The PowerPC's AltiVec, 128-bit vector processor is the undisputed first choice for DSP where floating-point performance is the critical decision point. However, the new breed of FPGA is geared up to wipe out the AltiVec advantage for the great variety of the military's fixed-point DSP applications. Interestingly, although the AltiVec has been available for some time and appears in Freescale Semiconductor's recently announced dual-core MPC8641D embedded processor, there does not appear to be any interest within the industry in offering competitive (and hence better or faster) floating point solutions for military DSP applications.

FPGAs with their innate parallelism appear set to oust the traditional multiple-PowerPC solution from a broad range of DSP applications. FPGAs offer much reduced real estate, power consumption, and cost. Time-to-deployment pressure from end users is driving some COTS vendors to offer prepackaged FPGA-based hardware/software products for specific application segments.

# Let's talk numbers

The advent of the latest generation of FPGAs such as the Xilinx Virtex-4 or the Altera Stratix II — having as many as 100,000 logic cells, 400 DSP Multiply/ Accumulate (MAC) elements and internal RAM, clocking at over 450 MHz — offers the potential to migrate and integrate DSP operations previously only performed by dedicated processors. The ability to process multiple data streams in parallel sets the FPGA solution apart from dedicated DSP or PowerPC alternatives.

Where ultimate performance is required on a single channel, the FPGA will always lose out. The AltiVec can perform a 64 x 64 MAC at single instruction rates (typically 1.5 GHz), whereas the FPGA will achieve 450 MHz for an 18 x 18 MAC. The FPGA's aggregate throughput from 400 MACs on multiple channels can far exceed that of a single PowerPC processor device in most applications. The DSP system designer can now choose from a number of design directions:

# Front-end processing of multiple array sensors

Unlike a PowerPC or dedicated DSP processor, an FPGA offers many MAC elements to perform operations in parallel on incoming data streams. Previously this kind of parallelism required many PowerPCs to perform repetitive tasks such as filtering and decimation from each array of the sensor, with the attendant data distribution challenges. This data distribution is simple if all the PowerPCs are located on, for example, just a single VMEbus card, but much more complex if they are spread among many cards or even racks of cards where switched fabrics would be required. Using FPGAs can bring about big reductions at the critical front end, typically offering savings equivalent to one FPGA per 10x PowerPCs. Power, weight, space, complexity, and cost are conserved.

# Complete system-on-chip fixed-point DSP solutions

The FPGA provides a versatile set of external interface options such as LVDS, PCML, LVPECL, and HyperTransport with which to build multiple types of sensor interfaces. The DSP and logic elements can be used for filtering and FFT operations, plus onboard hard and soft processor cores and real-time operating systems are available for logical and system-level operations. Extensive tool kits and libraries are available for the development of FPGA architecture, routing, and software to suit the final application requirement.

With the notable exceptions of multiplearray radar and sonar applications, most military applications for DSP are relatively straightforward and can be closely coupled to the sensor itself. Typical of this class of application are:

- Video and image processing

- Communications (SDR)

- Weapons system sensors such as torpedoes, cruise missiles, groundto-air missiles, air-to-air missiles, or surveillance UAVs.

Unlike the multiple-array radar and sonar applications that often use many hundreds of PowerPC-class processors plus a switched fabric for interconnection, these simpler applications listed above could be implemented by dedicated DSP devices such as the TigerSHARC, ASICs, FPGAs, or by a much smaller number of PowerPC processors.

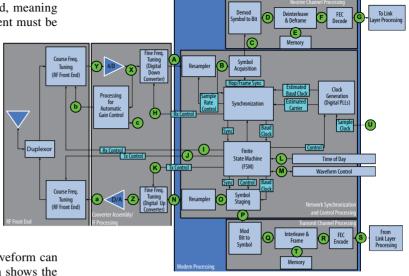

## **SDR** example

A potential application for a single FPGA device could be to form the basis of a typical rugged, man-portable SDR with multiple secure voice and data channels. Soft FPGA cores are available for filtering, and IFFT/FFT modulation and demodulation using the FPGA's DSP elements, plus encryption and decryption — thus providing a number of communication channels in just one FPGA device. To offer complete, system-level functionality, this configuration needs to be augmented with external interfaces to the RF components and the user, plus a general-purpose processor for operation of the user interface and regular diagnostics/prognostics of the completed system. Required user interfaces are:

- Serial RS-232/422 channels

- Ethernet

- USB

- Discrete I/O

An ideal packaging solution for an FPGA front-end is the PMC module. Most generic SBCs from established military

# In the System⊸

Figure 1

COTS vendors support the PMC concept of I/O, as indeed do many PowerPCbased DSP cards. The PMC module is independent of the SBC's processor type or bus architecture (for example VMEbus or CompactPCI), making it a versatile platform for many different applications. In this example, if the FPGA were implemented on a PMC-fomat module. it could then be mounted on a COTS 3U CompactPCI host SBC with either a Pentium or PowerPC processor. This combination of SBC and PMC would form the digital portion of the radio and would only occupy a single 0.8" slot width, 6.3" deep and 4" high.

# Time-to-deployment of new FPGA designs

Time-to-deployment of new technology has become a critical factor in the military procurement process. Whereas projects would once take many years to reach combat status, with what was by then obsolete technology, timescales have shrunk. Introducing new capabilities such as security and surveillance now demands not just the latest technology but all the tools and application support required for their immediate use.

Though SOC FPGAs promise the benefits of technology leadership, there is considerable development effort required to reach deployment when undertaking new application designs. This requirement is so even if it is based on a typical off-the-shelf solution such as a PMC module

using the FPGA manufacturer's toolkits. Some COTS vendors have taken the idea further and developed prepackaged applications for their FPGA. PMC modules that include standard hardware interfaces and application-ready code can be used

in areas such as SDR and video compression-based surveillance. Bundled COTS products reduce time-to-deployment to satisfy new expectations.

The TS-MPEG-4 bundled product from SBS Technologies shown in Figure 1 illustrates this product packaging strategy. It is based on a standard air- or conduction-cooled PMC module with an Altera Stratix EP1S30 FPGA, 128 MB of SDRAM, and a PCI interface to the host SBC. This PMC can be used in its basic form in many different applications with the customer developing code to suit. The external interfaces can be tailored by means of a unique micro-mezzanine mounted on the PMC module itself.

In the module's bundled form, the deliverable product includes all the code required for operation out of the box, plus physical interfaces to two RS-170 video sources and one RS-170 video output. Instead of using DSPs or general-purpose processors such as AltiVec-equipped PowerPCs, the supplied FPGA code compresses the two incoming video channels using MPEG-4, offering 15 to 20 percent

# In the System

better compression ratios than the widely used MPEG-2 standard. The card then streams compressed data over the PCI bus to the host SBC. On the host, the MPEG-4 stream is encapsulated and passed to a network connection using UDP. Remote display clients supplied with the bundle can then decompress and display the decoded video streams. It should be noted that this is an FPGA-based system, reaping all the benefits of FPGAs that we've been describing.

# Surveillance UAV example

Battlefield surveillance UAVs such as the Altair Predator B variant (Figure 2) are good examples of where packaged PMCbased FPGAs like the TS-MPEG-4 could be used for video capture and compression. This class of UAV usually flies at low to medium altitude over a battlefield or other area of particular interest and carries a number of video and, possibly, high-resolution single-shot cameras for a more detailed view of individual objects. The UAV will be controlled from a ground station that receives images from various cameras and displays them for analysis by the ground crew. The images may then also be relayed further up the command chain to build a complete tactical

picture of the battlefield. The downlink from the UAV to the ground does not have the bandwidth to transmit all the video streams directly from the cameras in real time, driving the need for compression.

The mission computer for such a UAV is likely to be implemented using COTS VMEbus or CompactPCI modules. Because of the limited space, weight, and power budgets available in a UAV, 3U CompactPCI would again be an ideal format choice for the mission computer. FPGA-based PMC modules for video compression could be mounted on a host SBC or could occupy 3U slots using carrier cards. Video streams direct from the cameras in RS-170 format would be converted to MPEG-4 by the FPGAs. then encapsulated and downlinked by the mission computer for any of the groundbased operations required.

The FPGA with its unique and flexible architecture looks set to replace many of today's dedicated DSP solutions where its parallelism and aggregate throughput make possible big reductions in real estate and cost. Equally, the cost of time-to-deployment is becoming a critical factor for both the government and system inte-

grator, and FPGA-based solutions often provide benefits as well. The availability of bundled, application-oriented COTS solutions, even though they may require minor customization for a particular enduse, promise to bring new FPGA-based DSP systems online faster and at lower

Duncan Young has worked in the defense industry for almost 40 years. Duncan was part of the management buyout team that formed Radstone Technology, and he initiated product development of conduction-cooled VMEbus modules. He has also served on a number of standardization committees. Duncan is now an independent consultant and writes this column on behalf of SBS Technologies.

For more information, contact: **SBS Technologies** 2400 Louisiana Blvd. NE, Ste. 5-600 Albuquerque, NM 87110 Tel: 505-875-0600 Website: www.sbs.com

Figure 2

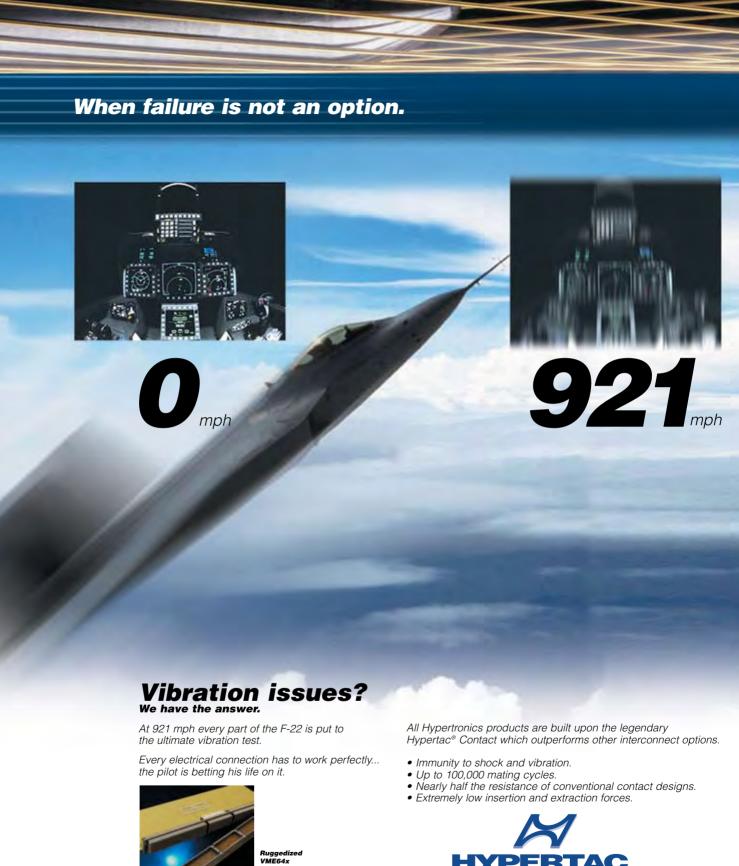

ISO 9001, 13485, & 14001 certified

and speed of data transfer are a necessity

smiths

Hudson, MA

1-888-HYPERTAC

www.hypertronics.com

# Why convert to a SAASM-based **Global Positioning System?**

By Ron Holm

In 1998, the Joint Chiefs of Staff selected the Selective Availability Anti-Spoofing Module (SAASM) as the security architecture to bring the Global Positioning System (GPS) to the next level, and issued the following mandate: As of October 1, 2006, all newly fielded Department of Defense (DoD) GPS systems will use SAASMcompliant Precise Positioning System (PPS) devices. Procurement of non-SAASM GPS user-equipment will be disallowed unless waived.

Despite a government mandate requiring all newly fielded DoD GPS systems to use SAASM-compliant PPS devices by October 2006, many military groups and other federal agencies continue to purchase receivers without SAASM compliance. Military users purchasing a GPS receiver without SAASM, or anyone who waits until the October 2006 deadline, is taking a security risk. Standard GPS service could be denied at any time via warfare tactics such as jamming or spoofing, and if this occurs, GPS receivers without SAASM will find it difficult to correct the situation quickly because the process to acquire SAASM-compliant receivers requires significant time for authorization and processing.

We are going to explain what SAASM is all about, why it's important to GPS receiver end-users, and why those who deploy non-SAASM receivers are putting their organization at risk right now - even though the deadline is less than a year away.

### Sense of urgency

The need for improving GPS security came to the forefront even more this past December in an announcement by President George W. Bush in which he issued the Space-Based Positioning, Navigation, and Timing (PNT) policy. The PNT policy authorizes the improvement of the United States' capabilities to deny hostile use of any space-based positioning,

navigation, and timing services without unduly disrupting civil and commercial access. In the policy, the President specifically directed the Secretary of Defense to develop and maintain navigation warfare capabilities required to effectively utilize GPS services in the event of jamming or other interference by adversaries.

This announcement underscores the fact that the federal government is increasing the level of urgency to safeguard GPS. The pressure for government agencies and military units to convert to SAASM-compliant GPS receivers is bound to also increase dramatically. Along with the selection of SAASM by

the Joint Chiefs, the writing on the wall is clear: All defense agencies should begin converting to SAASM GPS receivers.

# SAASM explained

To understand the risks and why it's important to deploy SAASM-compliant GPS receivers as soon as possible, a brief recap of GPS and SAASM will help. GPS has come to play a significant role in our everyday tasks during the past decade. GPS makes it possible to pinpoint the precise location of any person or place, anywhere in the world. It helps with everyday things such as how to drive our vehicles from Point A to Point B via onboard navigation systems.

# Spoofing and encrypted coding

GPS spoofing involves the intentional sending of a fake GPS signal by a simulated satellite mimicking a legitimate GPS satellite. Spoofing produces a false reading in GPS SPS devices and, if properly executed, can introduce position and timing errors, disrupting navigation and communication systems.

The low-power GPS satellite transmitters deliver extremely low-strength signals (equivalent to 0.00000000000000001 watt) to Earth-based GPS receivers that are vulnerable to jamming and spoofing. Jammers are inexpensive, unintelligent electronic devices that merely produce a higher-power blocking signal at the GPS frequency. Jamming is disruptive but usually detected by the GPS receiver as it stops tracking satellites. Spoofing requires more sophisticated, expensive equipment. Spoofing poses a particular security risk as it is often undetected by a GPS SPS device.

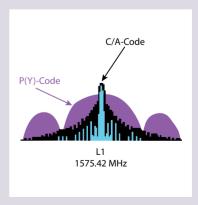

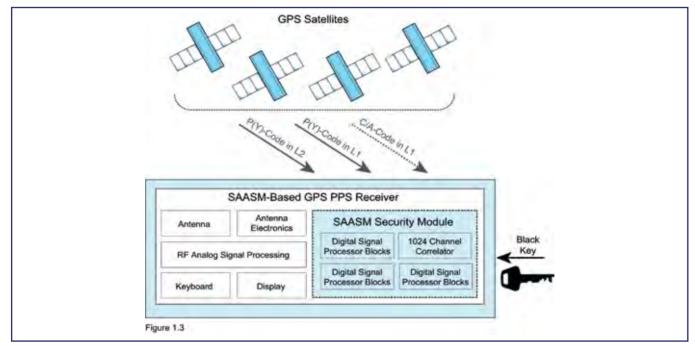

The key to preventing spoofing is to deploy a GPS receiver that can acquire encrypted GPS signals referred to as P(Y) coded signals, which are more robust and jam resistant. GPS satellites broadcast two signals: a civilian, unencrypted signal (referred to as C/A) that all GPS receivers can access, and the military encrypted coded signal P(Y). GPS devices in compliance with SAASM can receive and decrypt the P(Y) code (when keyed), which authenticates that the signal originated from the GPS satellites. The code frequency ranges are shown centered about L1 in Figure 1.

GPS has also become critically important to the military to identify the whereabouts of friends and foes, and it plays a crucial role in the success of military operations by providing precise time and frequency to communication systems. This allows military units to synchronize movements and ensure they communicate over secure frequency bandwidths that change on an irregular basis to avoid detection by the enemy.

Since GPS relies on low-powered frequency waves traveling from satellites to GPS receivers on the ground, the technology also lends itself to intentional jamming by enemies as well as unintentional or intentional jamming by allies. For example, the Civil Coarse Acquisition (C/A) code signal may be intentionally jammed by the US and other allies to allow only SAASM and legacy P(Y) receivers to access GPS. GPS is also susceptible to enemy spoofing – the deliberate attempt to mimic a legitimate signal and introduce erroneous position and time information.

To combat this situation, the US government launched a program in the 1990s referred to as *SAASM*. SAASM deploys anti-spoofing measures using cryptography to protect authorized users from false satellite signals generated by an enemy. To understand the reasons for SAASM, it helps to have an understanding of the components of the GPS system used by people, organizations, and governments throughout the world.

# **GPS** mini-history

Through a satellite navigation system, GPS provides positioning and clock time to GPS receivers on the earth. Conceptualized in 1973, the first GPS satellite was launched in 1978, and in 1995 the system became fully operational. Today the system consists of 28 satellites orbiting 12,500 miles above the Earth.

GPS was originally intended as a military force enhancement system but now serves dual purposes: GPS has evolved to improve not only military security but also the accuracy of the position, velocity, and time of any object on earth – securely to military users and freely to civil users. GPS does this by offering two positioning services: Precise Positioning Service (PPS) for authorized military users only and Standard Positioning Service (SPS)

for everyone, including the military. SPS utilizes a simpler, unprotected C/A code that is openly available to commercial, civil, and military users.

The GPS signals are transmitted on two L-band frequencies: L1 (1575.42 MHz) and L2 (1227.60 MHz). The SPS service is provided on L1 and the PPS service on both L1 and L2.

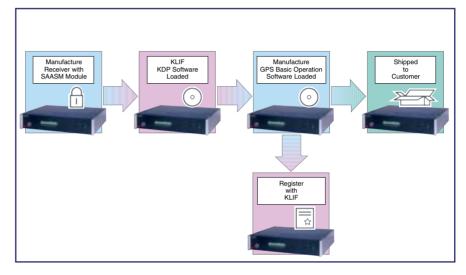

Manufacturers of SAASM GPS receiver modules and the products that they are integrated into, referred to as *PPS Host Application Equipment (HAE)*, must work closely with the Key Data Processor Loading and Installation Facility (KLIF) under strict guidelines. After manufacturing the SAASM unit, the GPS receiver manufacturer ships the SAASM hardware to the KLIF for the loading of the Key Data Processor (KDP) crypto software.

Figure 1

The DoD relies upon GPS as the primary source for position, navigation, time, and time synchronization. Therefore, the GPS network was also built to allow for the deployment of security measures. Selective Availability (SA) is a security technique that involves the introduction of intentional errors into the GPS signal. which denies full system accuracy to SPS users. On 2 May 2000, however, the effects of SA were set to zero and it appears unlikely SA will ever be set higher. But the potential still exists, and this would degrade the accuracy of GPS for SPS users. Anti-Spoofing (A-S) utilizes cryptography and special keys to protect a GPS PPS receiver from receiving false satellite signals generated by an adversary.

# The SAASM manufacturing and integration process

The detailed regulations that the US government has applied to the SAASM manufacturing process clearly demonstrate how serious GPS security has become and the need for immediate conversion to SAASM-compliant receivers.

After return of the SAASM device to the manufacturer, production test is completed and the unit is ready for sale to JPO approved customers.

Figure 1 shows the SAASM GPS receiver manufacturing process and integration into PPS HAE.

SAASM receivers support two key types to decrypt anti-spoofing and remove selective availability:

Physical-form red keys are classified, and distribution is closely protected since red keys are unencrypted.

Newer, black keys, on the other hand, are encrypted and unclassified. They can be distributed and loaded electronically, although paper tape distribution is still common. The decryption of the key only takes place within the secure SAASM module. Black keys may be renewable in the future via Over-The-Air-Rekeying (OTAR). Black keys make sense because they solve key distribution problems and are useless to

Figure 2

the enemy because they are encrypted. The DoD recognizes the security, delivery, and cost savings associated with black keys and wants users to transition from red to black keys as soon as possible (Figure 2).

To ensure security of the classified technology within a SAASM receiver and to preclude unauthorized procurement, the Navstar GPS Joint Program Office (JPO) at the Space and Missile Systems Center at Los Angeles AFB ensures compliance to DoD security requirements. All developers, integrators, and users of SAASM GPS must be JPO authorized.

SAASM developers and manufacturers must also meet several strict requirements, including securing a Communications Security (COMSEC) account, a KLIF account, and undergoing a complete JPO design-review process. Developers and manufacturers also have to prove they are free of foreign ownership, control, and influence and that they have a facility security clearance issued by the Defense Security Service (DSS).

Military end-users must receive authorization from the JPO to procure SAASM-based devices. When proper authorization occurs, the JPO issues a formal letter so that authorized manufacturers of SAASM GPS receivers will know authorization has formally been granted.

# Benefits of SAASM GPS receivers

By purchasing a SAASM receiver now, authorized users comply with the DoD GPS security architecture and possess the most secure GPS technology to enhance their ability to use precise positioning, velocity, and time in all environments. SAASM-based GPS receivers have the capability to directly acquire the encrypted, military GPS code and no longer have to depend on the often-jammed civil GPS code.

The need for deploying a SAASM receiver could become critical at any moment since access to the Standard GPS service (SPS) could be denied via warfare tactics focused on local and regional denial (jamming) of the civil code within an area of conflict. In addition to losing access to the signal, upgrading GPS SPS based systems to SAASM is nontrivial since the process to acquire product and distribute the keys that can decrypt coded signals requires significant time for authorization and processing.

Without a doubt, those military and government agencies that wait until the SAASM deadline approaches in October 2006 are taking a security risk. If an enemy source attempts to jam or spoof the GPS signal, users of non-SAASM receivers could lose all of their GPS capabilities.

Ron Holm is a product marketing manager for Symmetricom and manages the GPS Time and Frequency Instrumentation product line. Ron has been involved in the time

and frequency industry since 1990 and has held previous positions in engineering and engineering management. Ron holds a bachelor's degree in electronic engineering from the University of Minnesota.

To learn more, contact Ron at:

Symmetricom

2300 Orchard Parkway

San Jose, CA, 95131

Tel: 408-964-7619

E-mail: ttm\_sales@symmetricom.com

Website: www.symmetricom.com

The views expressed in this article are those of the author and do not necessarily reflect the official policy or position of the Navstar GPS Joint Program Office, the Air Force, the Department of Defense, or the U.S. government.

This article has been modified from the original October 2005 version to correct several technical inaccuracies. – Ed, July 2006.

# **Announcement and Last Call for Papers**

Experts from throughout the world are requested to submit a one page abstract\* describing the title, scope and content of the presentation while emphasizing the key points. Papers reporting on actual experience, knowledge and data gained from the use of commercial components and COTS in military and space systems are solicited. **Specific subjects for consideration include:**

- Design Practices

- Applications

- Case Studies / History

- Obsolescence Management

- Radiation Hardness

- Reliability Analysis & Testing

- Embedded COTS

- Technology Trends

- Risk Mitigation

- EEE Parts & Components

- Selecting COTS and Commercial Suppliers

\*Abstracts presented for consideration should be submitted before September 20, 2005.

CMSE 2006

February 6-9, 2006 Sheraton Gateway Hotel Los Angeles, California Organized by Components Technology Institute, Inc. For more information on the Conference or Exhibition please call 256-536-1304 or visit our web site at

www.cti-us.com

# Editor's Choice Products

# Rackmount PPC 970FX-based HPC does 64-bit Linux

Increasingly, low-cost cluster comput-

ers running open source Linux are being used in semi-benign military environments. The Mercury XR9 1U server is an example of one of these systems. Mercury effectively "bolted" together two PowerPC 970FX-based high-performance computing cluster nodes for efficiency and speed. The XR9 runs Terra Soft's 64-bit Linux OS Y-HPC and cluster management suite called *Y-Imager*.

The Mercury XR9 contains twin 2.4 GHz CPUs paired up to an IBM CPC925 Northbridge with a 16-bit 400 MHz HyperTransport cave, providing peer-to-peer access between processors, memory, PCI-X bridge, or the Southbridge. There are two independent PCI-X buses, three PCI-X slots, and dual Gigabit Ethernet ports. There are also four SATA channels, four USB 1.1 ports, and dual RS-232 channels. There's an optional InfiniBand PCI-X HCA with dual 4X ports, and an optional serial FPDP PCI-X HCA add-in for dual 2.5 Gbaud ports. A separate PowerPC 405EP performs "service and control," freeing the main CPUs for number crunching.

# **Mercury Computer Systems**

www.mc.com RSC #23086

# **Terra Soft Solutions**

www.terrasoftsolutions.com RSC #23087

# 256-channel digital down-converter fits into Gateflow FPGA library

In order to process wideband radio frequencies in digital systems, Digital Downconverters (DDCs) are used once the RF has been converted at the system front end. Trouble is, the areas of interest – the *channels* – have historically required lots of DDCs because of low channel density per device. Pentek aims to change all that with their Model 4954-430 256-channel narrowband DDC intellectual property (IP) core. Designed for use with Xilinx Virtex II, Virtex II Pro, or Virtex-4 FPGAs, the company claims this to be "at least an order of magnitude" higher channel count than any other implementation available in FPGA or ASIC form.

The high channel-to-FPGA ratio can reduce cost, weight, and space on circuit boards and in systems. 16-bit real or complex data can be accepted at up to 185 MHz. The architecture utilizes a channelizer stage that generates 1K fixed adjacent frequency channels with alias-free signals of greater than 75 dB across the passband (for each channel). The core includes a 256-channel output switch matrix that gives the user the ability to conduct "coarse tuning" between channels. An NCO performs independent tuning on each channel. Factory default filter coefficients are available, or users can create their own. The Model 4954-430 fits into Pentek's existing and well-proven Gateflow FPGA design kit, which includes cores for data acquisition, FFTs, FIR, radar pulse compression, and other general and specific functions.

### Pentek

www.pentek.com RSC #23089

# Hope for "classic" DS1691AJ/883 RS-422 drivers

When was the last time you saw a DIP-packaged IC?

If you deal with mil systems, you might've been

working with one of these babies as recently as

yesterday. That's because 10+ year military

life cycles require mature – and sometimes

obsolete – devices to be sourced for a long,

long time. We bring this to your attention because QP

Semiconductor makes a business out of being a "Military Integrated Circuit

Manufacturer" for QML and older SMD (DESC) devices. It may not be glamorous, but it's essential to our warfighters.

The company recently announced redesigned and replacement versions of the DS1691AJ/883 RS-422/423 line drivers, which originally came in both MIL-STD-883C and DESC 5962-8672101EA versions. Redesigned to match the original National Semiconductor 50V bipolar process devices, the replacement versions will be marked as QP1691AJ and are expected to be available as form, fit, and functional replacements for the originals. QP Semiconductor is performing a ground-up redesign; initial simulation models have been "successful," and the devices are in layout. Firm delivery dates will shortly be announced. The company maintains more than 1,540 ICs in their QML portfolio.

### **QP Semiconductor**

www.qpsemi.com RSC #23088

# Palm-sized vehicle computer – small as an "ROC"

It was bound to happen – marrying the successful stacked concept of PC/104 modules with conduction cooling for harsher environments. Done

using conduction-cooled PMC and PrPMC modules by COTS supplier SBS Technologies, the company's Rugged Operation Computer (ROC) is designed for those tiny available shoehorn spaces found in every system. Weighing just six pounds and consuming only 100 in², the ROC is ruggedized for use in UAVs, ground vehicles, or even soldier/Marine portable use. SBS is targeting avionics, vetronics, and navtronics applications.

Available CPU modules include Intel or PowerPC processors on PrPMCs from SBS. I/O ranges from the company's broad line of PMC I/O, plus all industry-standard conduction-cooled PMC cards. The ROC accepts an integral stacked PMC structure, complete with a 100 W power supply, EMI filter, and a CompactFlash disk with up to 128 GB of memory mounted on a PMC carrier module. Operating systems range from Windows XP and Linux to INTEGRITY and VxWorks. This is one ROC you'll want to throw at your computing problem.

### **SBS Technologies**

www.sbs.com RSC #23090

# **Enabling military design security** with high-performance FPGAs

By Joel Seely and Jie Feng

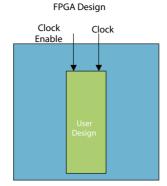

In an era of ever-increasing security concerns, SRAM-based FPGAs with a built-in configuration bitstream encryption feature offer critical advantages to military systems designers. In addition to high density, high performance, low development risk, and fast time-to-market benefits, they also deliver a secure approach for protecting designs against copying, reverse engineering, and tampering. For FPGAs without this built-in security feature, an additional nonvolatile device can be used to protect the FPGA design by supplying handshaking tokens.

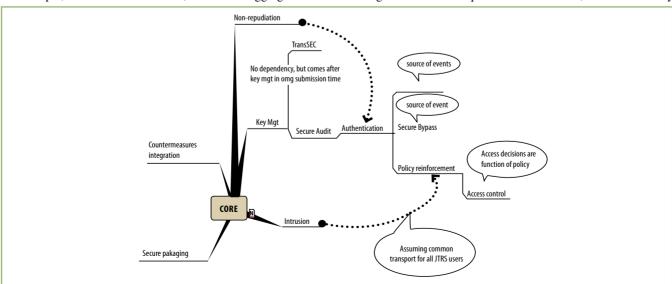

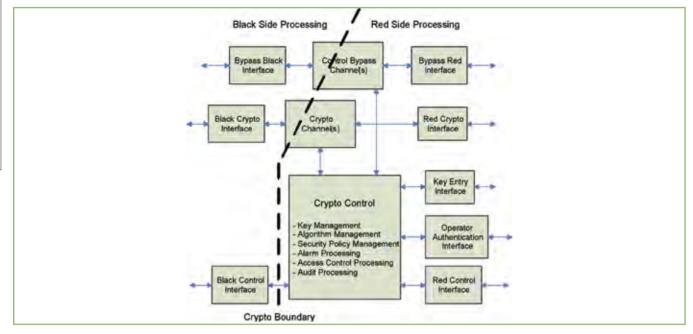

Military applications are becoming increasingly complex. Major programs such as Future Combat Systems (FCS) and the Joint Tactical Radio System (JTRS) are pushing technological capabilities on all fronts to their limits. The electronics in these systems are relying on programmable logic and FPGAs to provide extreme flexibility at a reasonable cost while not giving up the requisite computational power. For example, secure communication systems are used to connect a variety of airborne, space, ground- and sea-based military communication networks. They are used in the transmission, processing, recording, monitoring, and dissemination functions of a variety of such networks, including secure data links. All this functionality requires processing power and reconfigurability.

SRAM-based FPGAs provide the highest density, performance, and most advanced features among all FPGAs, and they are reconfigurable. However, SRAM-based FPGAs are volatile and require external Flash memory or configuration devices to store their configuration data. At power-up, the configuration data is sent from the memory device to the FPGA, which can be intercepted. Copying, reverse engineering, and tempering are security concerns for these high-performance FPGAs used in military systems.

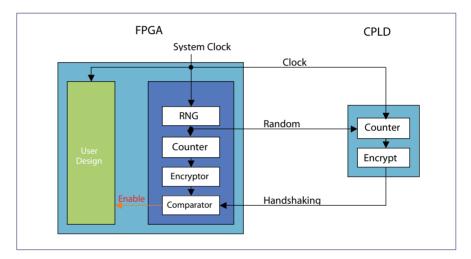

Two techniques – configuration bitstream encryption and handshaking tokens – can be used for securing designs within SRAM-based FPGAs. The configuration bitstream encryption is enabled using Advanced Encryption Standard (AES). Handshaking tokens are generated by a CPLD after communication with an FPGA. The FPGA only operates when the handshaking tokens from the CPLD match what it generates internally; otherwise, the design will shut down.

Let's investigate these techniques and how they secure SRAM-based military systems.

# Configuration bitstream encryption

Some of the latest generations of SRAM-based FPGAs contain built-in AES decryption engines and key storage for configuration bitstream encryption. A generic flow of secure configuration can be carried out in the following three steps:

- 1. Load the AES decryption key into the EPGA

- 2. Encrypt the configuration file with the same AES key and store it in the external memory, such as a configuration or Flash device.

- 3. At system power-up, the external memory sends the encrypted configuration file to the FPGA, which then uses the stored key to decrypt the configuration file in real time and configure itself.

AES comes in three different key sizes: 128-bit, 192-bit, and 256-bit. To understand the level of security, studies have shown that if one could build a machine that could discover a Data Encryption Standard (DES) key in seconds, it would take that same machine approximately 149 trillion years to discover a 128-bit AES key. (Source: National Institute of Standards and Technology)

Security key storage, which can be in either a volatile or nonvolatile location. is an important part of overall security. When the key is stored in volatile memory, an external backup battery is required when the power is down. Reliability, especially in military environments, is a major concern. Battery life depends on temperature and moisture levels of the surrounding area. If the battery dies, the key will be lost, and the device becomes unusable and must be sent back to the factory for repair. Batteries are often not desirable in military applications because of the possibility of leakage, outgassing, explosion, or going dead at an inopportune time. In addition, a battery increases overall system cost and requires special manufacturing attention. A nonvolatile key, which is more reliable, practical, and flexible, can be programmed during regular manufacturing flow with the FPGA either on- or off-board.

With configuration bitstream encryption, only encrypted configuration files and an AES key are stored in the system. Even if the configuration bitstream is captured, it cannot be decrypted without knowing the key. There are various ways to hide the AES key, including placing it under layers of metals in a distributed manner. Some FPGA vendors such as Altera also utilize additional security techniques to make the key difficult to find. Further, Altera does not support read back of the configuration file, whether it is encrypted or not. This adds another layer of security to the solution, making it very difficult to copy a design.

# Other security breaches

Reverse engineering any FPGA design to a Register Transfer Level (RTL) or schematic format through configuration bitstream is very difficult and time-consuming, even without encryption. For high-performance FPGAs, the configuration file contains millions of bits. To reveal the mapping from the configuration

# Hardware

file to the device resources, one needs to reverse engineer the FPGA or the FPGA development software. Some FPGA vendors do not disclose the configuration file formats, making reverse engineering more difficult. With configuration bitstream encryption, one needs to first find the key and decrypt the file. It may be easier and quicker to build a design from scratch than to reverse engineer a secured FPGA design.

Tampering is modifying the design stored in the device or replacing it with a different design. The tampered device may contain harmful design code capable of causing a system to malfunction or steal sensitive security data. Tampering cannot be prevented if a volatile key is used because the key is erasable; once the key is erased, the device can be configured with any configuration file. For the nonvolatile key solution, the device can be set to only accept configuration files encrypted with the stored key. A configuration failure signals possible tampering with the configuration file during transmission between the external memory and the FPGA, or during remotely communicated system upgrades. This is another advantage of a nonvolatile key.

# Handshaking tokens

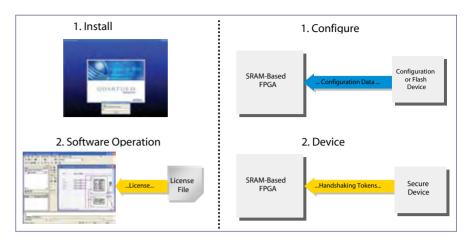

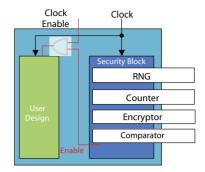

Configuration bitstream encryption is only available in high-density, high-performance SRAM-based FPGAs. The following solution allows any FPGA designs to remain secure against copying, even if the configuration bitstream is captured. This is accomplished by disabling the functionality of a user design within the FPGA until handshaking tokens are passed to the FPGA from a secure external device. The secure external device generates continuous handshaking tokens to the FPGA to ensure that it continues operation. Figure 1 compares the software license scheme with an FGPA security scheme.

Configuring the FPGA is similar to installing software onto a computer; the configuration bitstream is not protected. The external secure device is similar to the license file. The software will only operate when a valid license file is present. The user design within the FPGA will only operate when the handshaking tokens sent from the external secure device are valid. A simplified hardware implementation for this FPGA security solution is shown in Figure 2. In this example, a

Figure 1

Figure 2